芬兰坦佩雷大学和企业在开创性项目中开发出首款片上系统

芬兰坦佩雷--(美国商业资讯)--由芬兰SoC Hub联盟开发的首款片上系统(SoC)已经流片。项目合作伙伴接下来将专注于改进SoC的设计、自动化和性能。该联盟将开发三款芯片,第一款将于2022年初做好部署准备。项目有助于增强欧洲的技术主权。

此新闻稿包含多媒体内容。完整新闻稿可在以下网址查阅:https://www.businesswire.com/news/home/20211213005527/en/

芬兰SoC Hub已着手将SoC设计领域发展成为欧洲的先锋,并提高芬兰的竞争地位。去年,芬兰坦佩雷大学和诺基亚共同发起了SoC Hub倡议。合作伙伴开展的共同创造活动远远超出了传统研究项目的范围。

坦佩雷大学SoC设计副教授Ari Kulmala表示:“开发这款SoC的方法与工业生产所使用的方法相同,例如可测试性设计、广泛的验证以及关注系统级集成而非单个模块。”

Kulmala指出,该芯片带有一个开发工具包,能够集成到各种其他系统中,因此还可以由外部利益相关方进行测试。

SoC Hub项目的主要目标之一是实现新构思的快速原型开发,例如,在物联网(IoT)、机器学习和硅中的5G及6G技术。

新流片的Ballast芯片是三款芯片系列中的第一款。该芯片将由全球首屈一指的半导体芯片制造商台积电制造。

该芯片采用台积电新近开发的22纳米超低漏电工艺制造,特别适合物联网和边缘设备。Ballast包含若干不同的RISC-V CPU内核、一个数字信号处理器、一个人工智能加速器、丰富的类似传感器的接口和一个连接FPGA的扩展接口。另外,芯片还实施了一个包括驱动程序、软件开发工具和芯片调试支持在内的完整软件堆栈。该芯片同时支持实时操作系统和Linux。

imec(一家纳米与数字技术研发中心)旗下的imec.IC-link业务开发总监Bas Dorren表示:“我们很高兴能与SoC Hub团队合作。他们开发芯片的速度非常快,工作质量也堪称一流。”

未来两年内还有两款芯片流片

虽然芯片尺寸较大,但却在短时间内制作完成。得益于良好的团队精神和相关专家的专长和经验,这个宏大的目标最终得以实现。

坦佩雷大学计算机科学系主任Timo Hämäläinen表示:“为了实现大学与企业合作伙伴之间的无缝协作,我们做了大量工作。一些早期职业研究人员参与了Ballast的设计,因此有机会将他们从研究中获得的知识应用到工业项目中。”

除了SoC的开发之外,项目的第一阶段也是一项重大任务,它包括建立联盟和准备必要的软件和许可协议。该联盟由坦佩雷大学和诺基亚领导,合作伙伴包括CoreHW、VLSI Solution、Siru Innovations、TTTEch Flexibilis、Procemex、Wapice和Cargotec。

在这个由芬兰国家商务促进局(Business Finland)资助的项目中,三款SoC将在2023年底前流片。项目联盟将对芯片用例进行规划。

Timo Hämäläinen强调:“在项目的下一个阶段,我们将能够更多地关注SoC的系统、自动化和性能。尽管已经实现了我们的第一个目标,但我们将立刻继续推进项目。投资SoC开发的时机是现在,而不是未来。”

关于坦佩雷大学

坦佩雷大学是一座多学科综合性大学,也是芬兰规模第二大的大学。我们的研究和学习由三大方向引领:技术、健康和社会。该大学致力于解决人类社会面临的各项重大挑战并创造新的机会。其研究几乎涵盖了所有国际认可的领域。坦佩雷大学和坦佩雷应用科学大学共同组成了坦佩雷大学社区,拥有超过3万名学生和近5,000名教职员工。www.tuni.fi/en

原文版本可在businesswire.com上查阅: https://www.businesswire.com/news/home/20211213005527/en/

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

联系方式:

咨询:

SoC Hub联盟

sochub@tuni.fi

Timo Hämäläinen

坦佩雷大学计算机科学系主任

timo.hamalainen@tuni.fi

Ari Kulmala

坦佩雷大学片上系统设计副教授

ari.kulmala@tuni.fi

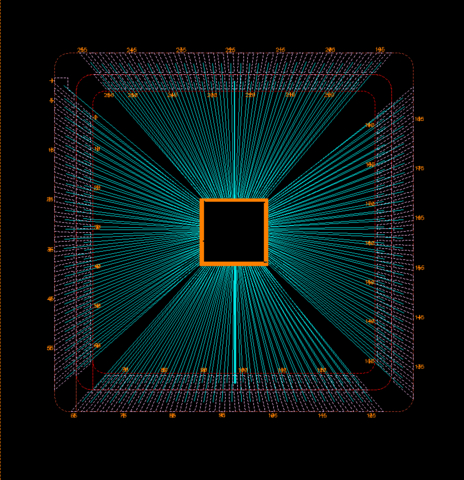

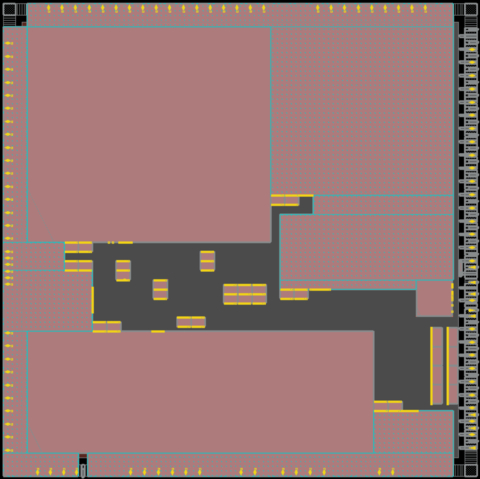

粘合图图像显示芯片IO Pad如何连接到封装引脚。封装被焊接到印刷电路板上。布局图显示功能块在芯片上的物理位置。侧面显示与封装引脚相连的IO Pad。照片:SoC Hub。(图示:美国商业资讯)

SoC Hub的运营基于坦佩雷大学和企业之间的创新合作。项目小组成员在坦佩雷大学合影。照片:Jonne Renvall/坦佩雷大学(照片:美国商业资讯)

粘合图图像显示芯片IO Pad如何连接到封装引脚。封装被焊接到印刷电路板上。布局图显示功能块在芯片上的物理位置。侧面显示与封装引脚相连的IO Pad。照片:SoC Hub。(图示:美国商业资讯)

(责任编辑:ysman)